The case for RISC-V IoT devices was once ideological. Open-source architecture, no licensing fees, freedom from ARM’s royalty structure. It was a compelling pitch, but largely an abstract one for most IoT product teams working within established supply chains. That conversation has changed considerably in 2026, and the reason is not philosophical. It is financial.

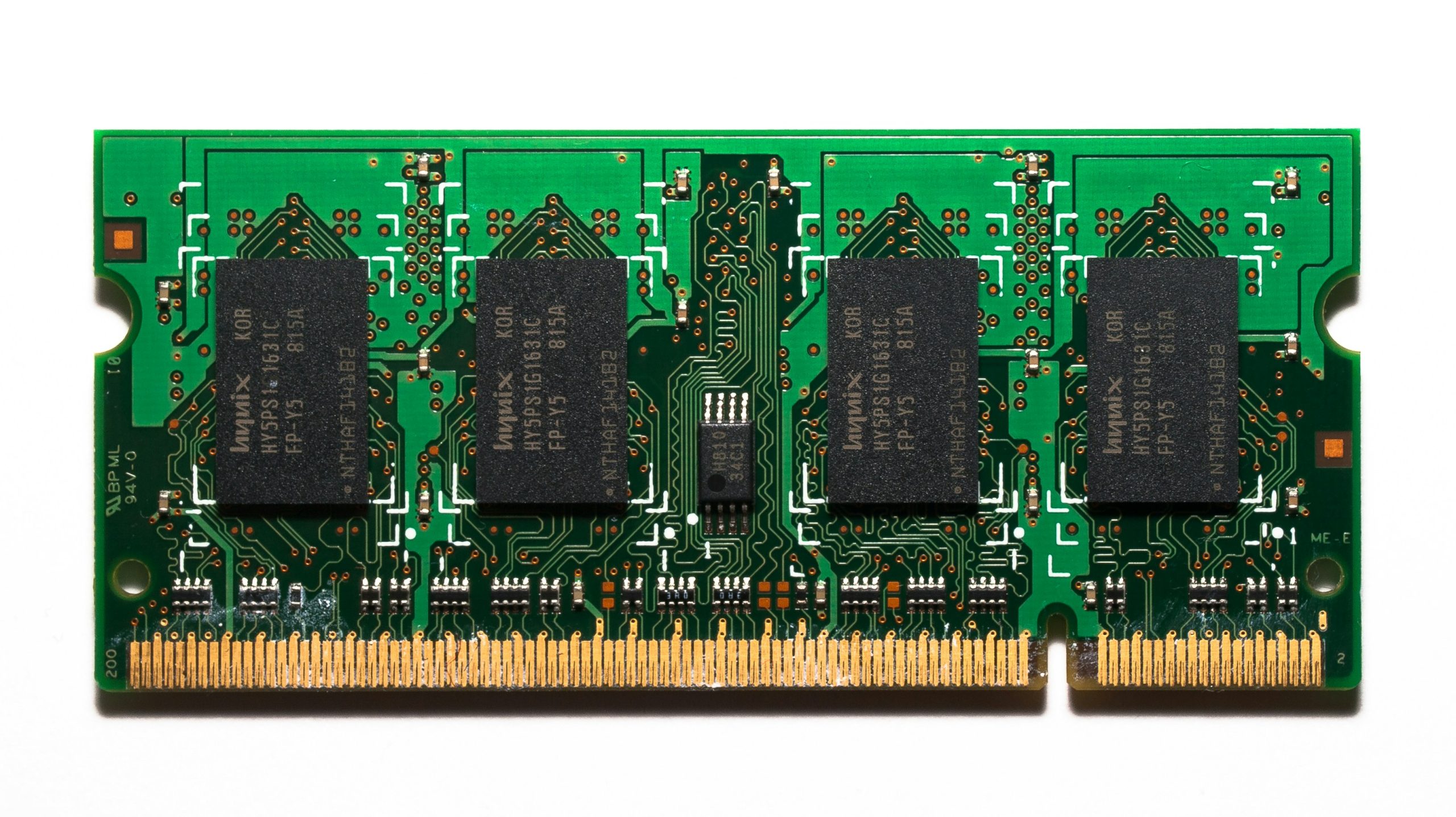

DRAM and NAND prices have surged to levels not seen in a generation. Samsung raised contract prices for certain memory chips by as much as 60% compared to September 2025 levels, according to Reuters. Micron has described the supply bottleneck as “unprecedented” and has exited the consumer memory market entirely to focus on higher-margin enterprise and AI customers. SK Hynix has reported that its HBM, DRAM, and NAND capacity is essentially sold out for 2026.

According to IDC, this is not a cyclical correction. It is a structural reallocation of silicon wafer capacity toward AI data centre infrastructure, one that could persist well into 2027. For IoT device makers, that backdrop changes the economics of chip architecture directly and immediately.

Every design decision that reduces memory dependency, lowers bill-of-materials cost, or avoids proprietary licensing exposure is worth more now than it was 18 months ago. RISC-V, the open-source instruction set architecture that began as a UC Berkeley academic project, has been quietly moving into exactly that position.

From niche to necessary

The RISC-V market was valued at US$2.49 billion in 2025 and is forecast to reach US$10.77 billion by 2030, a CAGR of 34%, according to Research and Markets. IoT devices accounted for 34.52% of RISC-V revenue in 2025, making it the architecture’s single largest application segment by share, according to Mordor Intelligence.

Asia-Pacific, which commands 42% of the current market, is where the growth trajectory is steepest, driven by regional chip-sovereignty programmes and the sheer volume of connected device manufacturing concentrated there.

The architectural fit for IoT is straightforward. RISC-V cores, particularly 32-bit variants, are designed for constrained environments where power consumption and memory footprint need to be small. Unlike ARM or x86, which bundle fixed instruction sets regardless of whether a device needs them, RISC-V allows engineers to build only what a product actually requires.

That modularity translates directly to leaner silicon, lower memory requirements, and a design that is less exposed to the commodity memory price swings currently hammering consumer electronics OEMs.

The inflexion point IoT analytics flagged

IoT Analytics identified 2026 as the inflexion point when IoT OEMs would begin scaling from early edge AI pilots to broad portfolio refreshes, with RISC-V adoption cited as one of the key architectural shifts accompanying that transition.

The firm noted that rising cost pressures and the need for flexible architectures were driving IoT semiconductor design away from monolithic SoCs toward modular chiplet designs and open-instruction-set cores. That prediction is now playing out against a memory market in crisis, which gives the cost argument additional urgency.

There is also an edge AI dimension to this. As IoT devices are increasingly expected to run local inference rather than offload processing to the cloud, the ability to add custom AI extensions to a RISC-V core without paying per-unit royalties becomes a meaningful cost lever at scale.

Nordic Semiconductor’s nRF92 Series, announced at MWC 2026, integrates Axon NPUs for edge AI alongside its cellular IoT capabilities–a design philosophy that reflects where the market is heading. Whether vendors reach that outcome through RISC-V or proprietary cores, the underlying pressure to do more on-device with less memory and lower licensing cost is the same.

The remaining friction

The case for RISC-V IoT devices is not without friction. The software ecosystem, while maturing rapidly, still carries a long tail of toolchain gaps and limited backward compatibility compared to ARM’s entrenched developer base. For product teams with existing firmware built on ARM or established vendor SDKs, the migration cost is real.

Research and Markets noted that software complexity from fragmented ISA extensions and a shortage of senior EDA talent in mature process nodes remain headwinds for broader adoption.

There is a geopolitical layer here, too. China accounted for a significant share of global RISC-V shipments in 2025, driven in part by government mandates to reduce dependency on Western proprietary architectures in critical infrastructure.

The EU’s DARE initiative–Digital Autonomy with RISC-V in Europe–has already produced its first AI unit for industrial robotics. For IoT vendors navigating an increasingly fragmented trade environment, the question of which chip architectures can be sourced without geopolitical exposure is no longer theoretical.

None of this means RISC-V will displace ARM in IoT overnight. ARM’s installed base, toolchain maturity, and commercial support infrastructure are formidable advantages that do not evaporate because memory prices are high. But the conditions that once made RISC-V a long-term consideration have compressed into a short-term economic argument. When memory is expensive and scarce, lean and license-free starts to look less like an ideology and more like good engineering.

The AI memory crisis did not create the RISC-V story. But it may be the thing that finally forces the IoT industry to take it seriously.

(Photo by William Warby)

See also: Powering smarter IoT: Nordic Semiconductor and edge AI

Want to learn more about IoT from industry leaders? Check out IoT Tech Expo taking place in Amsterdam, California, and London. The comprehensive event is part of TechEx and co-located with other leading technology events. Click here for more information.

IoT News is powered by TechForge Media. Explore other upcoming enterprise technology events and webinars here.